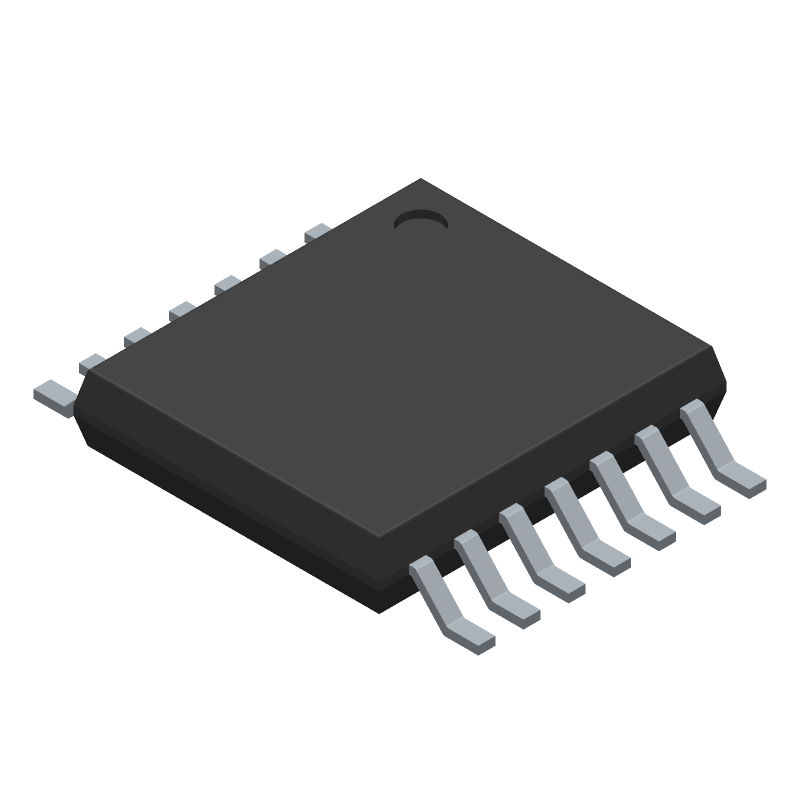

The 74LVC32APW-Q100J is a dual OR gate IC from Nexperia, featuring a 14-pin TSSOP package. It operates over a temperature range of -40°C to 125°C and is compliant with AEC-Q100. The device has a supply voltage range of 1.65V to 3.6V and a propagation delay of 10.4ns. It is designed for use in automotive applications and has a terminal position of dual.

Quick Jump:

Technical Specifications

Nexperia 74LVC32APW-Q100J technical specifications.

General

| Max Operating Temperature | 125 |

| Number of Terminals | 14 |

| Min Operating Temperature | -40 |

| Terminal Position | DUAL |

| JEDEC Package Code | R-PDSO-G14 |

| Width | 4.4 |

| Length | 5 |

| Pin Count | 14 |

| Number of Functions | 4 |

| Temperature Grade | AUTOMOTIVE |

| Supply Voltage-Nom (Vsup) | 3.3 |

| Supply Voltage-Max (Vsup) | 3.6 |

| Supply Voltage-Min (Vsup) | 1.65 |

| Logic IC Type | OR GATE |

| Family | LVC/LCX/Z |

| Propagation Delay (tpd) | 10.4 |

| Number of Inputs | 2 |

| Screening Level | AEC-Q100 |

Compliance

| REACH | Compliant |

| Military Spec | False |

Datasheet

Nexperia 74LVC32APW-Q100J Datasheet

Download the complete datasheet for Nexperia 74LVC32APW-Q100J to view detailed technical specifications.

This datasheet cannot be embedded due to technical restrictions.